approfondimenti

55

Viterbi Complex Unit (VCU II)

La VCU II viene integrata nella CPU per ela-

borare

funzioni matematiche complesse

in

maniera efficiente. Questa unità accelera le

prestazioni degli algoritmi di comunicazione

fino a 10 volte e offre margini per la crescita

futura del sistema e velocità di bit superiori;

o, in alternativa, consente il funzionamento

dei dispositivi a velocità inferiori per ridurre i

costi e i consumi energetici dei sistemi. Negli

azionamenti industriali, la VCU II può miglio-

rare la previsione di guasti al motore tramite

l’analisi delle vibrazioni sui motori.

Acceleratore di controllo in tempo reale (CLA)

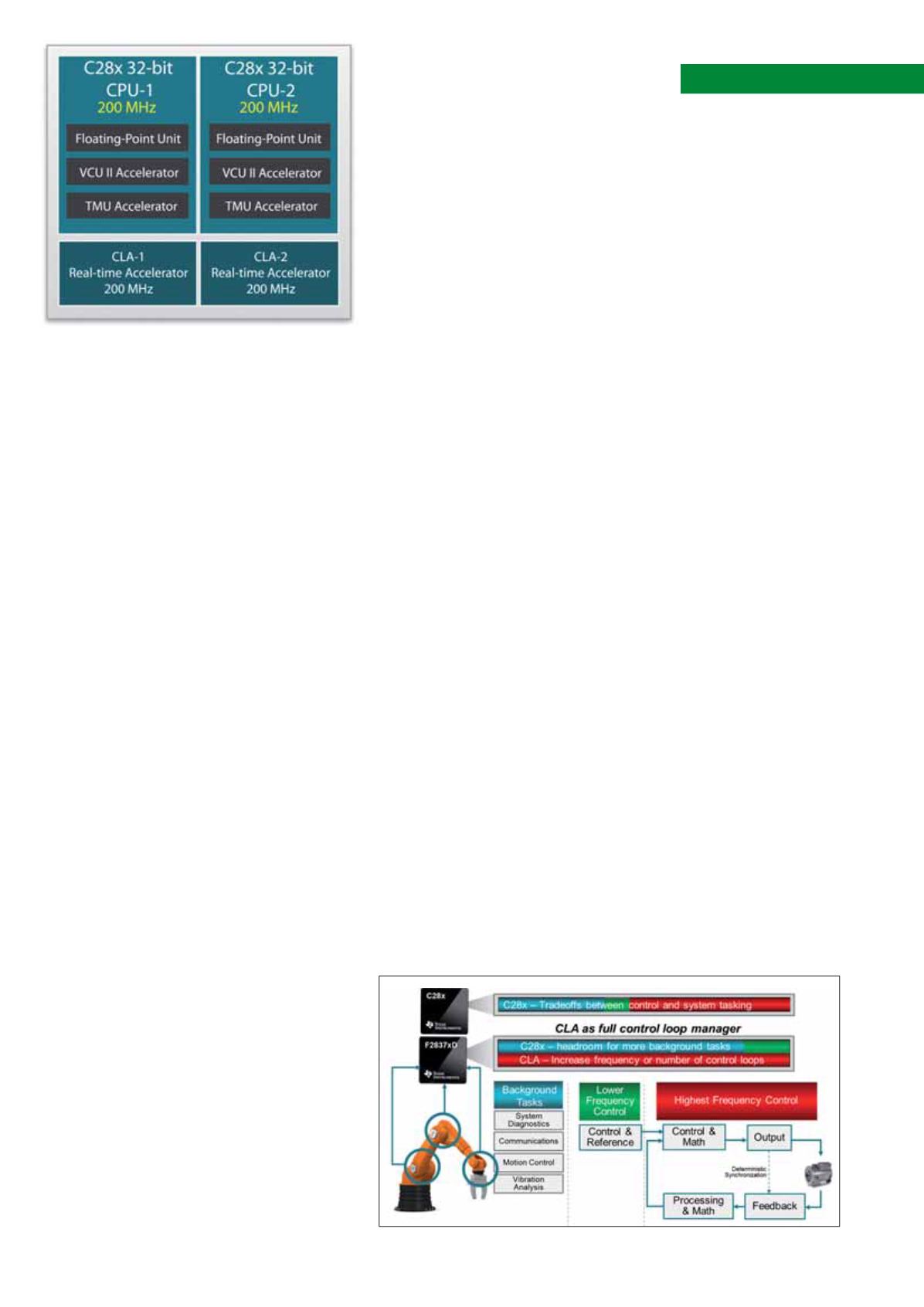

Le MCU F2837xD integrano due CLA in

tempo reale che consentono una ripartizione

intelligente delle attività di controllo critiche in

un sistema di azionamenti. I CLA sono

proces-

sori a virgola mobile

indipendenti con un’ar-

chitettura dedicata a bassa latenza simile a una

CPU e accesso diretto alle periferiche di con-

trollo. I CLA possono essere utilizzati in vario

modo per sgravare la CPU da attività intensive

di elaborazione di segnale

υ

figura 1

.

L’acceleratore può far parte del front-end di

un convertitore analogico-digitale (ADC) e

pre-elaborare i segnali in ingresso per filtrare

il rumore e immagazzinare i dati nella propria

RAM. In questo modo la CPU viene coinvolta

solo quando è disponibile un intero blocco

di dati pre-elaborati. Il CLA può effettuare

anche l’analisi del segnale su forme d’onda di

corrente in ingresso, la pre-elaborazione del

feedback, il controllo del feed-forward, l’ana-

lisi di segnali speciali, l’elaborazione di pac-

chetti e altro ancora.

Negli azionamenti industriali, una CPU + CLA

può implementare funzionalità sul lato di con-

trollo, ad es. l’anello di controllo della coppia,

mentre l’altra CPU + CLA implementa la parte

applicativa del sistema, ad esempio rileva-

mento di velocità e posizione, calcolo di tra-

iettorie e comparazione dei profili di moto. La

suddivisione del sistema di azionamento indu-

striale in porzioni di controllo e applicazione

assegnate alle due CPU consente una chiara

ripartizione che semplifica la progettazione.

Questo approccio contribuisce anche a bilan-

ciare le attività di controllo in tempo reale e di

applicazione

υ

figura 2

.

Bassa latenza e architettura

deterministica

Il determinismo è essenziale nelle applicazioni

di controllo. Con l’architettura di memoria non

condivisa (loosely coupled) tipica di un proces-

sore basato su cache, è difficile determinare le

peggiori condizioni (worst-case) di capacità di

risposta che determinano perdite imprevedibili

della cache. Tipicamente i progettisti fanno

affidamento sulla profilazione dell’esecuzione

in tempo reale del sistema per verificare le con-

dizioni di funzionamento peggiori. Eventuali

modifiche al codice del sistema possono richie-

dere che la profilazione venga ripetuta più

volte per verificare che i limiti deterministici

del sistema non siano stati superati.

L’architettura della MCU Delfino F2837xD

è costruita su una

base deterministica

. Gra-

zie alla sua architettura a memoria condivisa

(tightly coupled), non serve una cache e si eli-

minano i relativi ritardi dovuti a perdite della

cache. Tutte le transazioni di memoria verso

la RAM statica (SRAM), la memoria flash e le

periferiche sono studiate per essere compatibili

con la struttura e i cicli di bus finiti, offrendo

una capacità deterministica. La doppia perife-

rica di memoria ad accesso diretto a sei canali

aumenta l’efficienza di gestione della memoria,

assicurando che i dati siano sempre disponibili

quando la CPU o gli acceleratori ne hanno biso-

gno. Questo determinismo si estende anche alle

periferiche della MCU. La latenza dell’ADC è

nota, così come il tempo necessario alla CPU

per aggiornare i moduli PWM (modulazione di

larghezza d’impulso). Non è necessario sapere

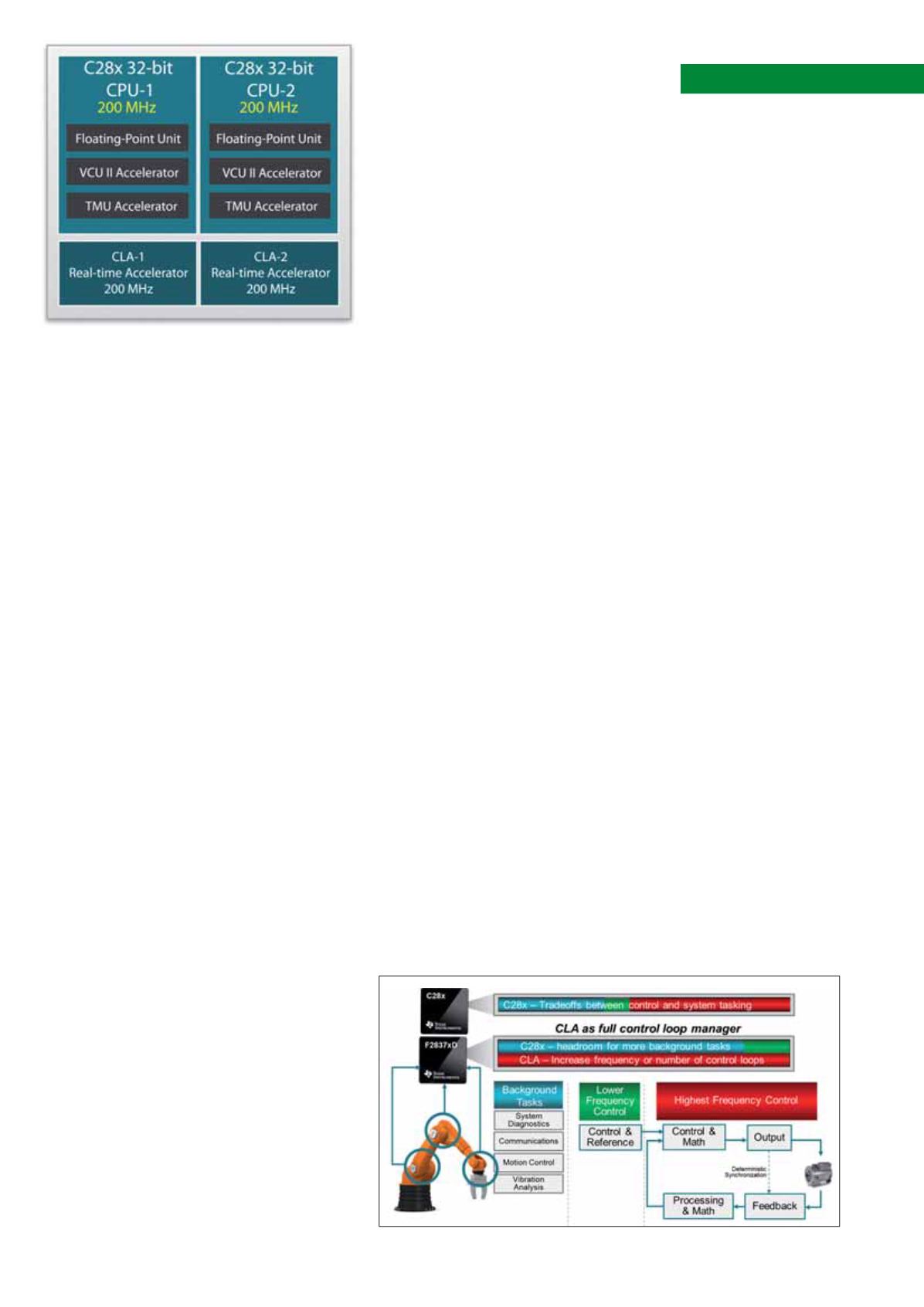

Figura 1 - Il CLA può aumentare la

frequenza o il numero degli anelli

di controllo, sgravando la C28x

in modo che possa svolgere più

attività di controllo in background

e attività di sistema

Figura 2 - Dettaglio dei core e degli acceleratori della CPU C28x.

Automazione e Strumentazione

■

Maggio 2014

CONTROLLO