ELETTRONICA

applicazioni

Automazione e Strumentazione

■

Maggio 2014

59

lazione e acquisizione classica come alimen-

tatori, I/O digitali e analogici, anche strumen-

tazione di analisi RF (analizzatori di spettro e

vettoriali,

transceiver

ecc.) e di acquisizione

veloce (oscilloscopi e digitalizzatori).

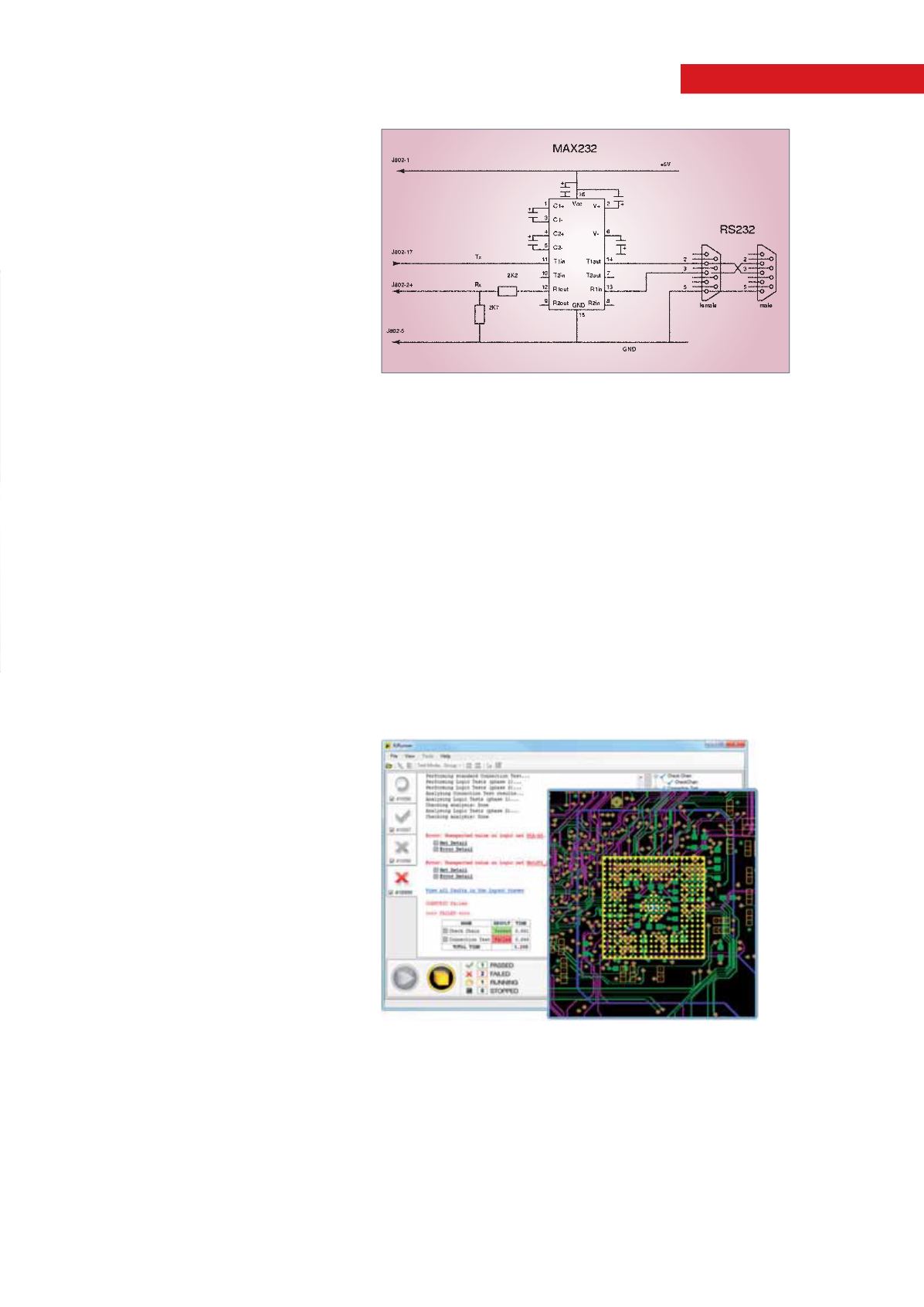

Confrontando le due tipologie di test e conside-

rando il caso semplice di un

driver

per interfac-

cia seriale Max202, tramite test ICT si potranno

verificare i valori dei condensatori della pompa

di carica, mentre con il test funzionale verranno

inviati e letti dei pacchetti dati.

Sino a poco tempo fa, quindi, il test ICT ha

permesso di verificare facilmente il corretto

montaggio di tutti i componenti prima che si

eseguisse il test funzionale. Tuttavia, la densità

di componenti spesso raggiunta nelle schede

non permette il posizionamento di un numero

sufficiente di

testpoint

e l’utilizzo sempre più

frequente di componenti BGA, difficilmente

accessibili una volta saldati – nonostante ci

siano tecniche basate sulla variazione della

capacità sviluppate per evitare di dover contat-

tare fisicamente i

pad

- rende sempre più

antie-

conomico o persino impossibile il test ICT

.

Il test Boundary Scan

La crescente complessità dei componenti elet-

tronici digitali ha invece reso sempre più pre-

sente l’interfaccia

Boundary Scan

che risulta

disponibile su tutti i componenti digitali di

ultima generazione come FPGA, microcontrol-

lori, RAM, convertitori.

Il Boundary Scan, seguendo lo standard JTAG

IEEE 1149.x, prevede una circuiteria all’in-

terno dei

chip

in grado di rendere disponibile

un protocollo di collaudo completo a livello di

scheda.

Tale circuiteria, adeguatamente implementata

dai chip

vendors

, prevede la sostituzione dei

probe

fisici con delle celle Boundary Scan,

denominate BSC. Le BSC simulano dei probe

virtuali per ogni ingresso e uscita presente sul

chip. Ogni cella permette di osservare il nor-

male flusso di dati attraverso i

pin

di I/O e con-

trollare lo stato del pin attraverso la comunica-

zione seriale della catena Boundary.

Il test Boundary Scan, anche se concettual-

mente molto diverso dall’ICT, permette di

verificare la corretta interconnessione di tutti

i componenti (assenza di corto circuiti tra le

piste e verifica continuità), oltre che la pre-

senza di molti componenti pur non potendone

verificare con esattezza il valore, anche se

alcune implementazioni funzionali sono possi-

bili per tutti quei componenti accessibili dalla

catena JTAG. Inoltre, il tool Boundary Scan è,

in moltissimi casi, anche utilizzato per la pro-

grammazione di questi componenti.

Il test ICT può quindi essere rimpiazzato in

molte parti del circuito con un test Boundary

Scan infinitamente meno invasivo:

quest’ultimo, infatti, richiede l’accesso alla

scheda tramite il solo connettore (o pads)

JTAG, già normalmente disponibile sulla

scheda per necessità legate al

debugging

a alla

programmazione. Tuttavia il test basato su

Boundary Scan non è in grado, per sua natura,

di testare completamente tutti i circuiti presenti

in una scheda elettronica: da solo non sarà mai

in grado di testare parti analogiche, così come,

più in generale, non potrà testare autonoma-

mente tutti i componenti sprovvisti di interfac-

cia Boundary.

Un approccio nuovo: il test funzionale

integrato con test Boundary Scan

Per poter testare in maniera completa un

sistema, è quindi indispensabile associare al

test Boundary Scan un test funzionale: in que-

sto modo non solo si è in grado di completare

il test del sistema in tutte le parti scoperte dal

Boundary Scan, ma si può poi eseguire il test

funzionale vero e proprio.

Schema di connessione

tipico del driver

Max232

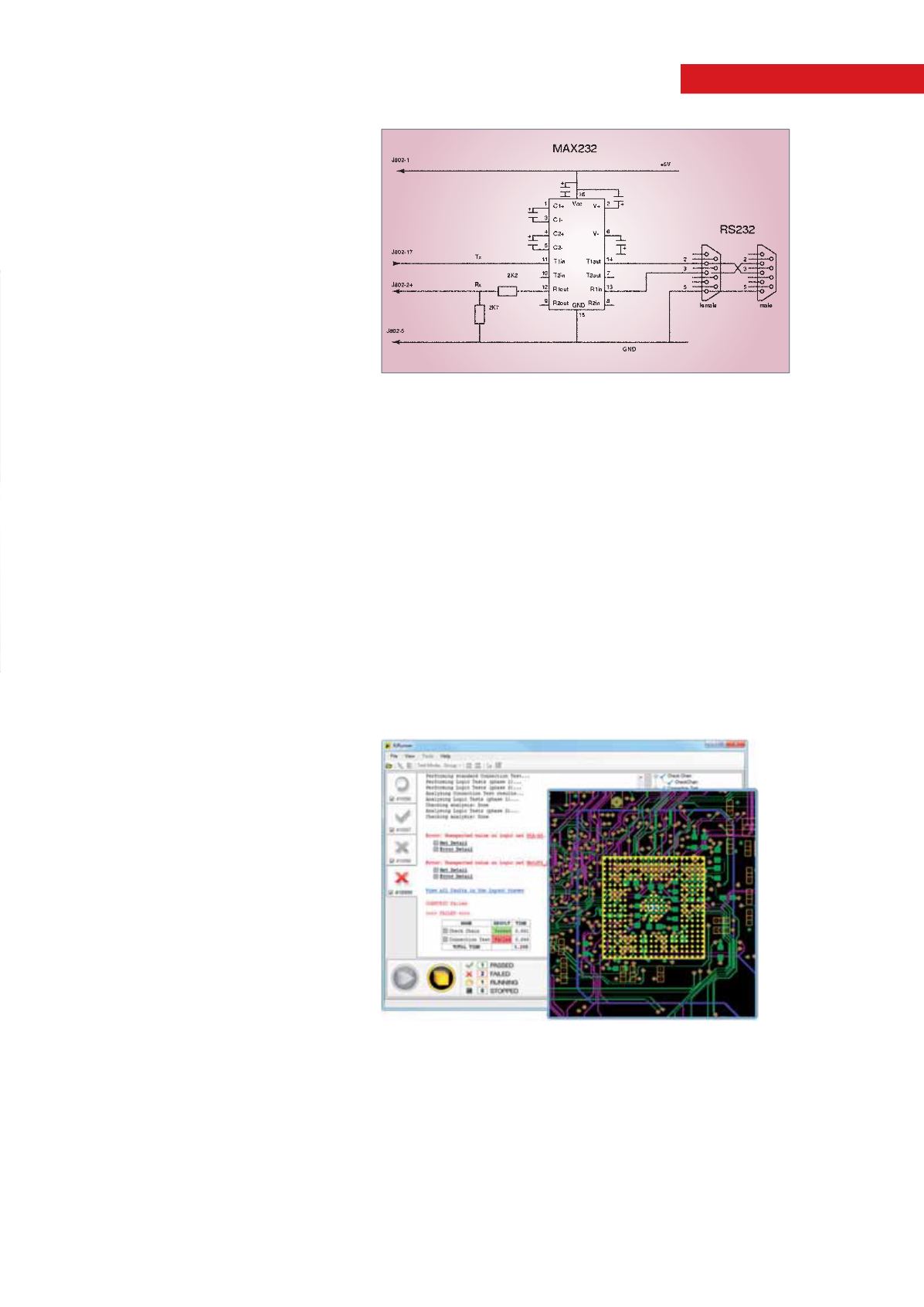

Esempio di software XJTAG

di test Boundary scan che

evidenzia i pad di connessione

di un chip