Trace32 supporta i nuovi Arm Cortex-A5

I debugger Trace32, di Lauterbach, supportano i nuovi processori Arm Cortex-A5

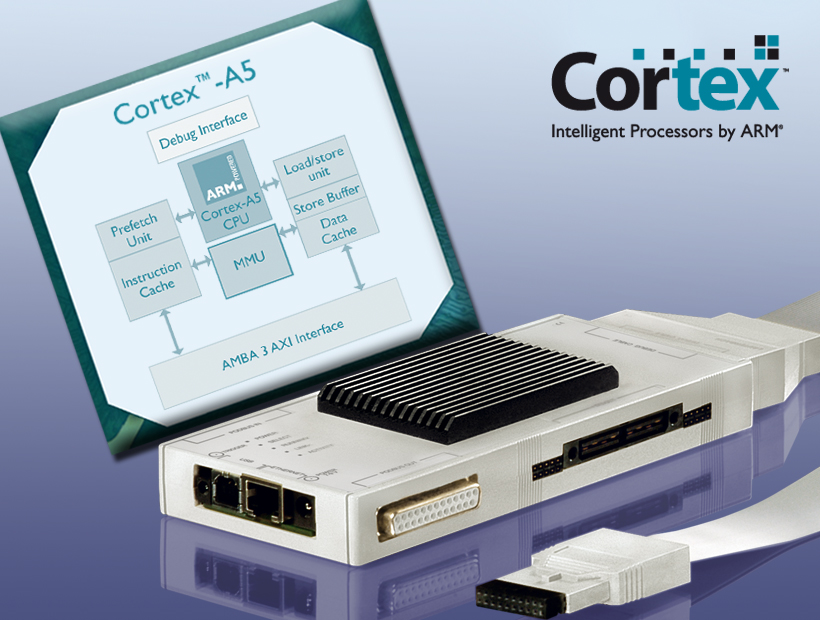

La nuova architettura microprocessore Cortex-A5 viene fornita sia nella versione a un solo core sia in quella multicore scalabile, Cortex-A5 MPCore, che consiste in un sistema di massimo quattro Cortex-A5 disposti in gruppo ed è progettata per applicazioni che necessitano di elevate performance e bassi consumi.

Grazie alla porta Etm, Cortex-A5 ha capacità di trace programma non intrusivo per tutti i core, consentendo la piena visibilità del flusso delle istruzioni eseguite e l’analisi e il profiling del sistema.

I sistemi Trace32, inoltre, supportano la tecnologia CoreSight per i Cortex-A5, estendendo le capacità di debug e trace per controllare l’intero system on chip, inclusi i core multipli Arm e Dsp.

Trace32 offre pieno supporto ai sistemi operativi più diffusi con possibilità Asymmetric Multiprocessing o Symmetric Multiprocessing.

Lauterbach: www.lauterbach.com

Contenuti correlati

-

Un approccio concorrente per la meccatronica del futuro

Al primo Benchmark Forum - Ingegneria Intelligente, un evento organizzato a Bologna dal consorzio LIAM, dal CRIT Research e dall’istituto tedesco ITQ, i protagonisti dell’automazione hanno risposto alle richieste dei costruttori di macchine per...

-

La versatilità del boundary scan per programmazione e debug

Lo standard JTAG IEEE 1149.1, definito da Joint Test Action Group, originariamente sviluppato per facilitare il collaudo strutturale delle schede assemblate, nonché per collaudare le schede nelle quali è impossibile realizzare un contatto fisico tra i piedini...

-

Mentor Graphics e Lauterbach insieme per una piattaforma di verifica SoC

L’unione della competenza e della tecnologia di due grandi colossi quali Mentor Graphics e Lauterbach ha portato all’implementazione di un’innovativa soluzione che facilita la produzione dei circuiti stampati. E’ una piattaforma ad alte prestazioni per lo sviluppo...

-

Lauterbach e Discretix si alleano per fornire un sistema di debug sicuro

In genere le interfacce di debug come JTAG sono disabilitate quando il chip lascia la fabbrica per assicurarsi che non ci siano possibilità di abuso da parte di hacker o altri soggetti non autorizzati. Ora il nuovo...